KOKUSAI ELECTRICの技術

当社グループは、半導体製造の数ある工程の中で、半導体デバイスの性能を左右する成膜プロセス、トリートメント(膜質改善)プロセスを軸に事業を展開しています。これらのプロセスには、枚葉式とバッチ式があり枚葉式がウェーハを1枚ずつ成膜するのに対してバッチ式は数十枚以上のウェーハを一度に成膜することができ高い生産性が特長です。これらのプロセス技術に対応する当社グループのバッチ成膜装置、枚葉トリートメント装置は世界中の半導体デバイスメーカーから高い評価をいただき、世界トップクラスのシェアを有しています。

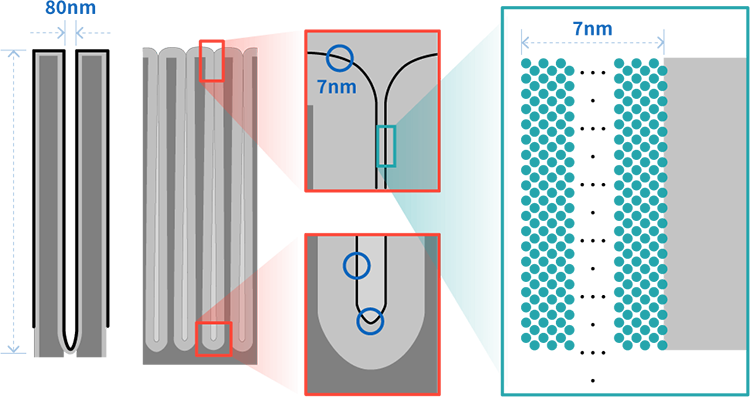

半導体デバイス市場は、従来のPCやスマートフォンなどのコンシューマ向けからデータセンタや次世代移動通信システム、AI※1などの高成長産業向けへと需要がシフトしながら拡大しており、これに伴い、半導体デバイスの構造は複雑化・三次元化が進んでいます。この半導体デバイスの進化に対応するため当社グループは、狭く深い高アスペクト比※2の溝や孔を多数持つウェーハに対応するナノレベルでの成膜技術や、プラズマや熱を加えることで膜質を改善するトリートメント技術を開発、進化させることで、世界の半導体デバイスメーカーのニーズに応えてきました。

こうした当社グループの技術は、熱流体力学、機械工学、制御工学、電気・電子工学、さらには、マテリアル工学、物理工学、プラズマ工学などの集大成であり、一朝一夕に培われるものではありません。私たちは、現状に満足することなくそれぞれの領域で日々技術を磨き、それらを融合することでお客様のニーズに対応するためのイノベーションを生み出しています。

バッチALD技術

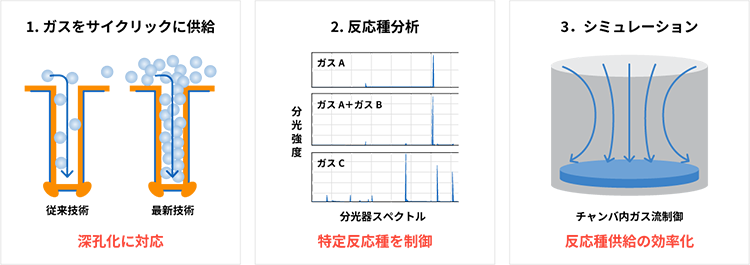

ALD(Atomic Layer Deposition)※3技術は、高品質な薄膜をステップカバレッジ※4良く形成することが可能な難易度の高い技術で、半導体デバイスの進化とともにニーズが高まっています。このALD技術は、複数のガスをサイクリックに供給するため、成膜に時間がかかり生産性に課題がありました。これに対し、一度に数十枚以上のウェーハへの成膜を可能とするバッチ成膜技術の生産性の高さが有効な解決策となります。ALD技術とバッチ成膜技術を融合した当社グループのバッチALD技術は、難易度の高い薄膜形成と高生産性を両立することで、高アスペクト比の溝や孔を多数持つウェーハに対しても、高い生産性で、ステップカバレッジに優れた成膜が可能となるため、半導体の進化への対応と幅広いアプリケーションへの展開を実現する最も論理的なソリューションと言えます。

トリートメント(膜質改善)技術

トリートメント(膜質改善)技術とは、成膜後にプラズマや熱を加えることにより膜中の不純物を除去し、粒子を安定させることで膜質を改善させる技術です。半導体デバイスの微細化・複雑化に伴い低温環境での成膜需要が高まっており、トリートメント技術は低温環境で膜質改善を可能にするソリューションとしても需要が拡大しています。

当社グループは、新しい手法を用いたトリートメント技術の開発に注力しており、厳しい条件下でも半導体デバイスが所定の性能を発揮できるよう既存の薄膜を高品質化するための処理手法を開発しています。例えば、反応種を豊富に供給するプロセスを開発することによって、200層以上の深孔を有する3D-NANDにおいてもステップカバレッジに優れた処理方法を提供し、主要メモリメーカーに採用されています。また、新しい原料を用いた反応種の種類や現象についてモニタリング、シミュレーションを行い、反応モデルを解析してより適切な処理方法の開発を進めています。

- ※1

-

Artificial Intelligence(アーティフィシャル・インテリジェンス)の略で、人工知能のことをさします。

- ※2

-

微細加工された半導体デバイスの形状における溝や孔の縦横比のことをさします。

- ※3

-

当社グループでは、複数のガスをサイクリックに供給する工程を伴い、原子層レベルで成膜する手法を「ALD」と呼んでいます。

- ※4

-

基板の表面にある微細な段差に成膜した際の、膜の被覆状態のことで、段差被覆性ともいいます。